취준 첫트에 취뽀 성공~!~!

정말 가고싶었던 삼성전자에 붙게 되어서 너무 행복하네여

이제는 진짜 학부생활 마지막 업로드 끝!

'취준일기' 카테고리의 다른 글

| 삼성전자 2021하반기 대졸공채 GSAT 합격자 발표 (0) | 2021.11.17 |

|---|---|

| 2021년 하반기 삼성전자 대졸공채 GSAT 준비중 (0) | 2021.10.26 |

| 2021 하반기 삼성전자 3급 신입채용(1) (0) | 2021.10.16 |

취준 첫트에 취뽀 성공~!~!

정말 가고싶었던 삼성전자에 붙게 되어서 너무 행복하네여

이제는 진짜 학부생활 마지막 업로드 끝!

| 삼성전자 2021하반기 대졸공채 GSAT 합격자 발표 (0) | 2021.11.17 |

|---|---|

| 2021년 하반기 삼성전자 대졸공채 GSAT 준비중 (0) | 2021.10.26 |

| 2021 하반기 삼성전자 3급 신입채용(1) (0) | 2021.10.16 |

과기대 와서 김성권교수님을 만난건 천운이라고 생각한다.

op-Amp부터 반도체, 전자회로1,2 응용전자회로 , 양자역학까지 너무 재밌게 배웠다.

이 어려운 전자공학 과목들을 완전히 이해는 못해도 즐기면서 배울 수 있었던건 교수님 덕분이라고 생각한다.

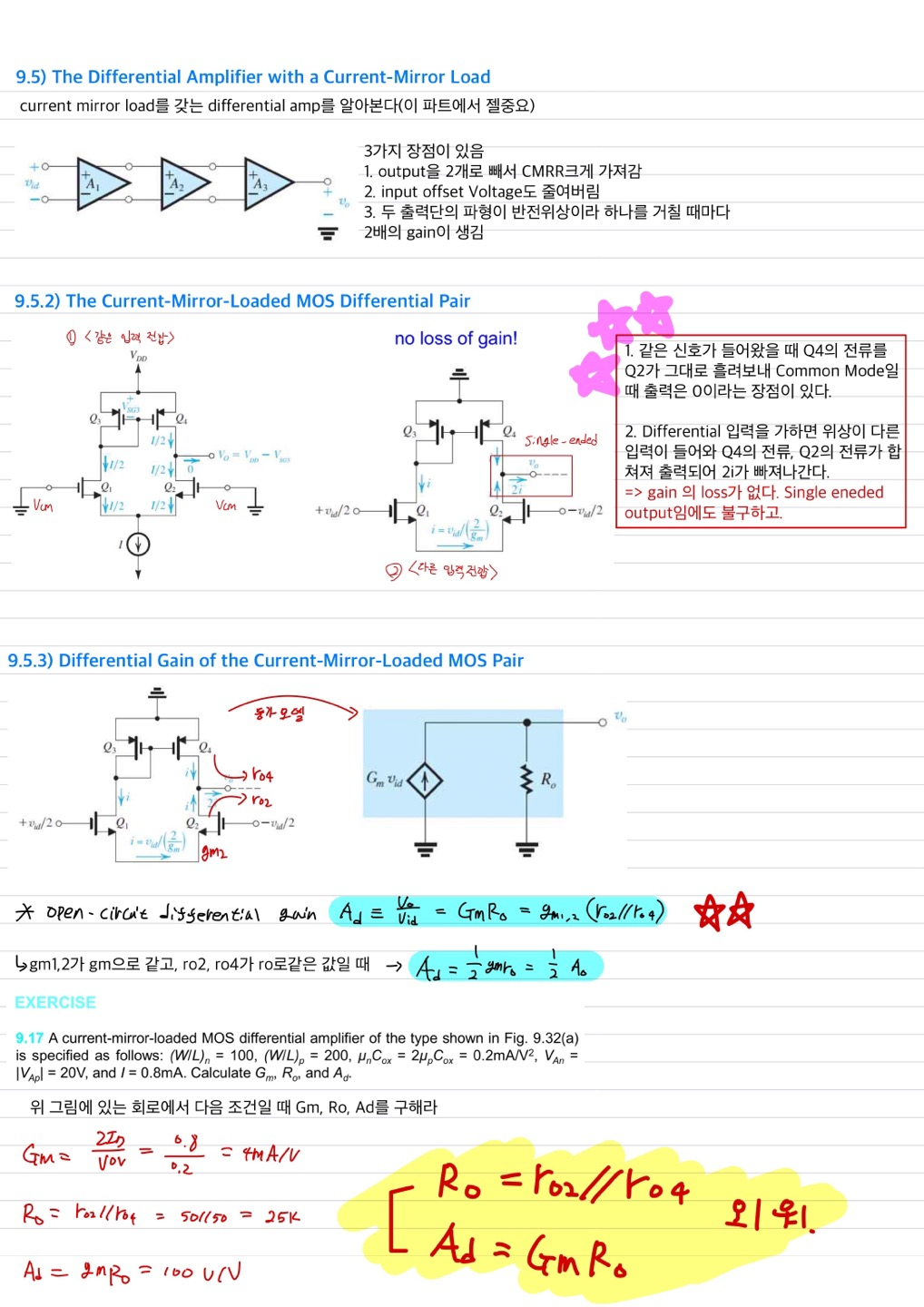

1. Operation with a Differential input Voltage

2. Large Signal Operation

3. Small Signal Operation - Differential Gain

- Differential Half-Gain

4. The Differential Amplifier with Current-Source Loads

5. Cascode Differential Amplifier

- Effect of RD Mismatch

- Effect of gm Mismatch

6. DC Offset

7. The Differential Amplifier with a Current-Mirror Load

8. The Current-Mirror-Loaded MOS Differential Pair

9. Differential Gain of the Current-Mirror-Loaded MOS Pair

10. Common-Mode Gain and CMRR

11. A Two-Stage CMOS Op-Amp

뒷부분 정리할 시간에 시험공부 해야해서 여기까지 정리하고 마무리하기

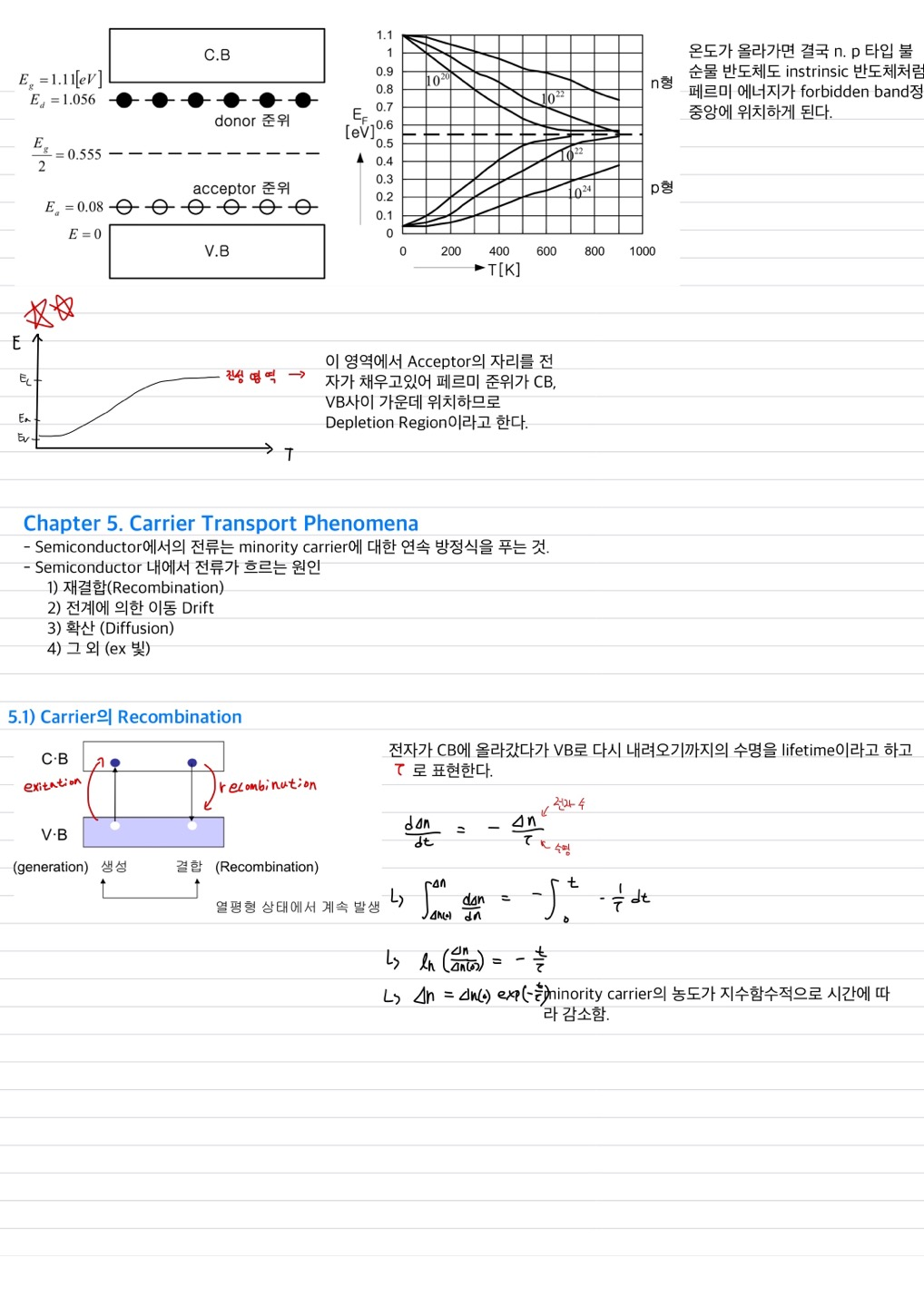

1. Position of Fermi-Energy Level

2. Fermi=Energy in Intrsinsic, Extrinsic Semiconductors

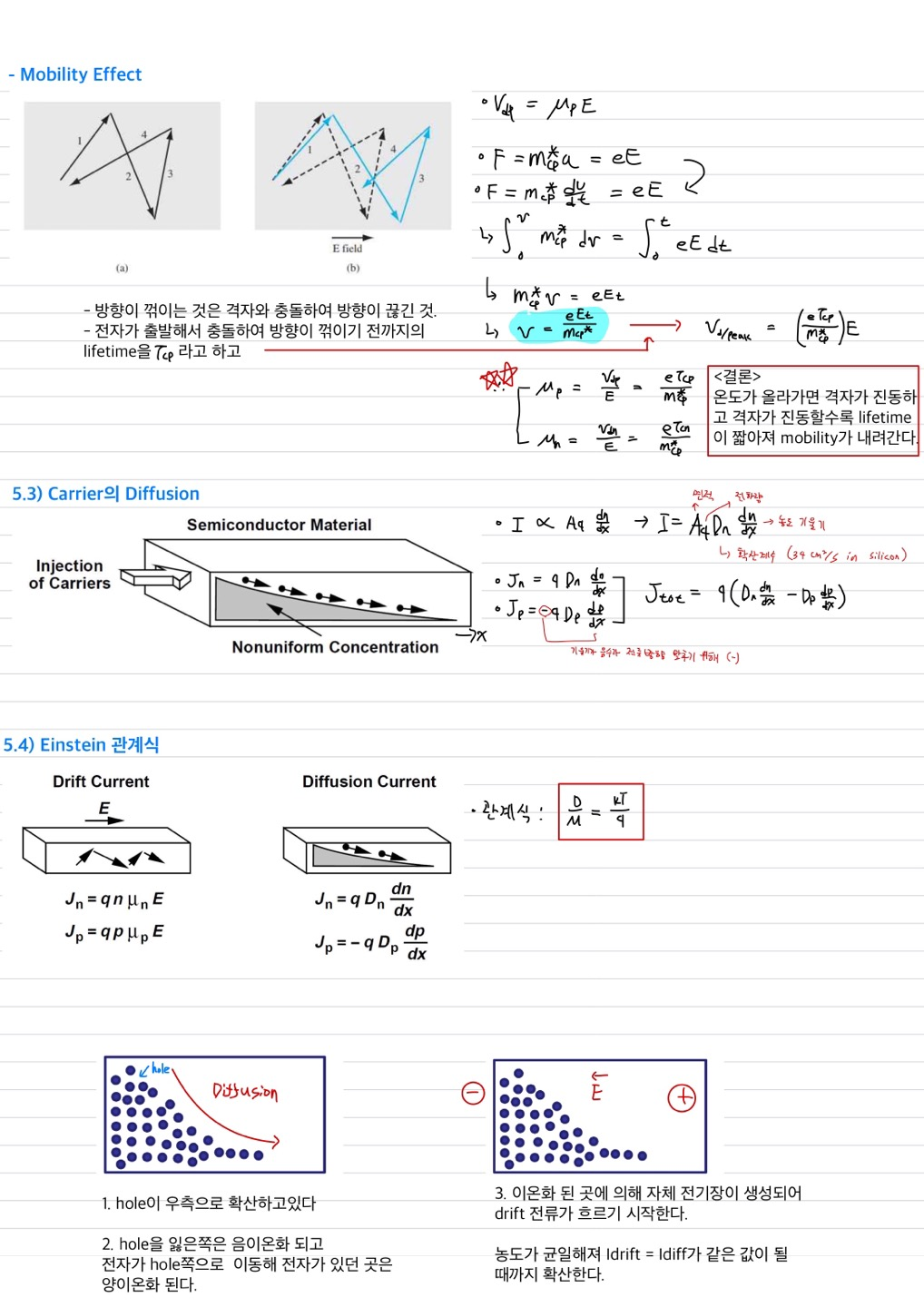

3. Carrier Transport Phenomena

4. Recombination

5. Drift Current

6. Diffusion Current

7. Einstein 관계식

8. Continuity Equation

| [반도체소자공학]week11. 양자역학(외인성 반도체 의 에너지,전자,홀 농도) (0) | 2021.11.23 |

|---|---|

| [반도체소자공학]week10. 양자역학(열평형상태의 전자-홀 농도, Intrinsic concentration, 전기전도) (0) | 2021.11.15 |

| [반도체소자공학]week9. 통계역학(Fermi-Dirac 분포함수), 평형상태의 반도체 (0) | 2021.11.10 |

| [반도체소자공학]week8. 양자역학(상태밀도함수), 통계역학(Fermi-Dirac Probability Function) (2) | 2021.11.09 |

| [반도체소자공학]week7. 양자역학(k-Space Diagram, Energy Band Structure) (0) | 2021.11.08 |

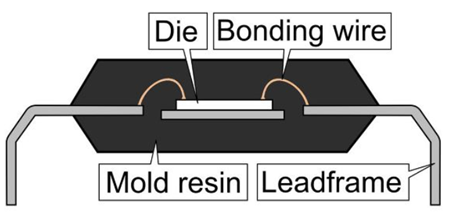

2. 패키징 과정

2-1. 웨이퍼 절단(Wafer Sawing)

웨이퍼를 낱개의 칩으로 분리하는 단계로 스크라이브 라인(Scribe Line)을 따라 웨이퍼를 다이아몬드 톱이나 레이저를 이용하여 절단한다.

2-2. 칩 접착(Die attach)

절단된 칩을 반도체 칩을 외부 회로에서 전기신호를 전달하고 보호해주는 리드프레임 또는 PCB로 옮긴다

2-3. 금속 연결(Wire Bonding)

2-4. 성형 공정(Molding)

2-5. 패키지 테스트 공정(Package Test)

- 테스트를 거쳐서 다양한 환경에서 칩의 신뢰성을 검증하고 그 과정에서 생긴 주요 이슈는 제조공정이나 조립 공정에 전달해 사전에 오류를 방지해 제품의 질을 향상시킬 수 있도록 한다.

• 제조공정이나 조립공정에 피드백 ▶ 제품 질 향상

2. TSV의 장점

3. TSV의 적용 분야

4. TSV의 요구 기술

5. TSV의 기술 동향

| [반도체 8대공정] 7. EDS공정 (0) | 2021.11.29 |

|---|---|

| [반도체 8대공정] 6. 금속 배선 공정 (0) | 2021.11.29 |

| [반도체 8대공정] 5. 박막 증착 공정 (0) | 2021.11.29 |

| [반도체8대공정] 3. Photo공정 (0) | 2021.11.29 |

| [반도체 8대공정] 2. 산화와 도핑 공정 (0) | 2021.11.29 |

2. EDS공정의 목적

1. 웨이퍼 상태 반도체 칩의 양품/불량품 선별

2. 불량 칩 중 수선 가능한 칩의 양품화

3. FAB 공정 또는 설계에서 발견된 문제점의 수정

4. 불량 칩을 미리 선별해 이후 진행되는 패키징 공정 및 테스트 작업의 효율 향상

3. EDS 공정의 5단계

1단계 - ET Test & WBI (Electrical Test & Wafer Burn In)

2단계 - Pre-Laser (Hot/Cold)

3단계 – Laser Repair & Post Laser

4단계 – Tape Laminate & Bake Grinding

5단계 - Inking

Inking 공정까지 끝난 웨이퍼는 건조된 후 QC Gate의 최종 검사를 거쳐 패키징공정으로 옮겨진다.

| [반도체 8대공정] 8. 패키징 공정(기본+TSV 공정) (2) | 2021.11.29 |

|---|---|

| [반도체 8대공정] 6. 금속 배선 공정 (0) | 2021.11.29 |

| [반도체 8대공정] 5. 박막 증착 공정 (0) | 2021.11.29 |

| [반도체8대공정] 3. Photo공정 (0) | 2021.11.29 |

| [반도체 8대공정] 2. 산화와 도핑 공정 (0) | 2021.11.29 |

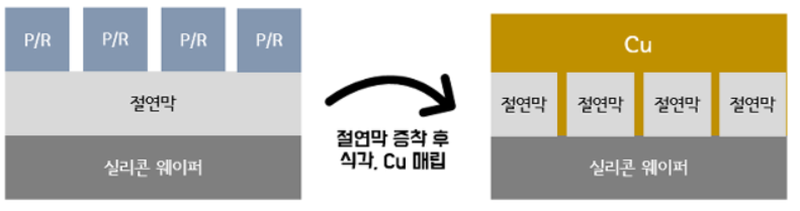

1. 금속 배선 공정(Metallization)이란?

- 포토, 식각, 증착 등 여러 공정을 반복하면 웨이퍼 위에 반도체 회로가 만들어진다. 이 회로가 동작하기 위해서는 외부에서 전기적 신호를 가해 주어야 하는데, 신호가 잘 전달되도록 반도체 회로 패턴에 따라 금속선을 연결하는 작업을 금속 배선 공정이라고 한다.

2. 금속 재료의 필요조건

1) 웨이퍼와의 부착성 : 실리콘(Si) 웨이퍼 위에 얇은 박막으로 증착 할 수 있도록 부착이 쉬워야 하며, 부착 강도 또한 우수해야 함.

2) 전기 저항이 낮은 물질 : 금속선은 회로 패턴을 따라 전류를 전달하는 역할을 하기 때문에 전기저항이 낮아야 함.

3) 열적, 화학적 안정성 : 금속 배선 공정의 후속 공정에서 금속 선의 특성이 변하지 않도록 열적, 화학적 안정성이 뛰어나야 함.

4) 패턴 형성의 용이성 : 회로 패턴에 따라 금속선을 쉽게 형성시킬 수 있어야 함. 아무리 좋은 금속이더라도 식각 등의 공정 특성에 맞지 않으면 반도체 배선 재료로 쓰이기 어렵다.

5) 높은 신뢰성 : 집적회로 기술의 발전으로 반도체가 미세화 됨에 따라 금속 배선 역시 작은 단면으로 제작해도 끊김 없이 사용할 수 있어야 함.

6) 제조 가격 : 위 조건을 만족시키더라도 제조 가격이 높으면 대량 생산이 어렵기 때문에 반도체의 재료로 적합하지 않다.

위 조건을 충족시키는 대표적인 금속은 알루미늄(Al), 구리(Cu), 텅스텐(W), 티타늄(Ti) 등이 있다.

3. 알루미늄(Al) 배선공정

1) 알루미늄 배선 공정 과정

-> Al 증착 ▶ PR Coating ▶ Photo ▶ Develop ▶ Al Etch ▶ PR Strip

2) 알루미늄의 장단점

| 알루미늄의 장점 | 알루미늄의 단점 |

| - 박막 상태에서도 bulk 상태와 비슷한 높은 전기전도도를 가진다. - 박막 증착이 쉽다. - 산화막과의 접착력이 좋다. - 사진, 식각 공정이 쉽다. -낮은 접촉 저항

-가격이 저렴하다.

|

- Hillock이 잘 형성된다. - 부식이 잘 된다 - 녹는점이 낮다. -CVD, 전기도금이 어렵다

-전자이동으로 수명이 짧다.

|

4. 구리(Cu) 배선공정

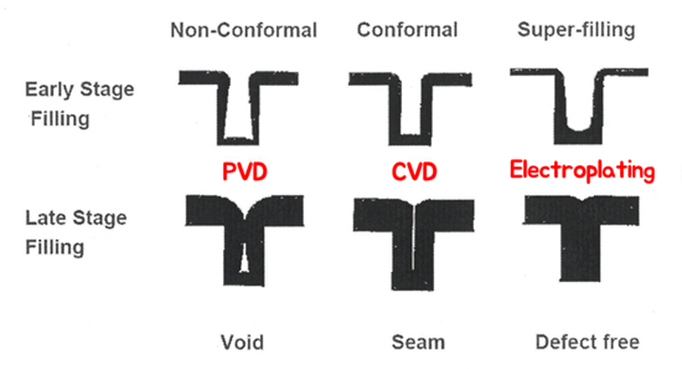

- 구리는 알루미늄이 텅스텐보다 비저항이 낮아, 같은 저항값을 갖는 금속선에 대해서 보다 미세하게 패턴 제작을 할 수 있어 사용되고 있다. 그치만 구리가 식각이 어렵기 때문에 구리를 먼저 증착하고 cmp공정을 통해서 깎는 다마신 공정을 통해서 구리선을 배선해야 한다.

1) 구리 배선 공정 과정

->SiO2 증착 ▶ PR Coating ▶ Photo ▶ Develop ▶ SiO2 Etch ▶ PR Strip ▶ Cu 매립 ▶ CMP

2) 구리(Cu) 장단점

| 구리의 장점 | 구리의 단점 |

| -Al보다 낮은 비저항 -Al보다 높은 녹는점 낮은 확산 계수 - Electromigration이 억제되어 신뢰성 향상 -낮은 RC Delay |

-Etch가 어렵다 (Damascene 공법으로 해결) -벤드 갭 때문에 Cu가 SiO2를 확산으로 지나감 → 회로가 고장 날 수 있음 (Diffusion barrier를 형성하여 해결) |

3) 구리 증착 방법

| [반도체 8대공정] 8. 패키징 공정(기본+TSV 공정) (2) | 2021.11.29 |

|---|---|

| [반도체 8대공정] 7. EDS공정 (0) | 2021.11.29 |

| [반도체 8대공정] 5. 박막 증착 공정 (0) | 2021.11.29 |

| [반도체8대공정] 3. Photo공정 (0) | 2021.11.29 |

| [반도체 8대공정] 2. 산화와 도핑 공정 (0) | 2021.11.29 |

1. 박막 증착(Thin film Deposition)

1) 박막 증착이란?

- 원하는 물질을 기판에 붙이는 것을 증착(Deposition)이라고 한다.

2) 왜 박막(Thin film)을 쓰는가??

2. PVD란?

- PVD(Physical Vapor Deposition)란 열 또는 충격과 같은 물리적 반응을 통해 박막을 표면에 증착하는 방식이다.

3. Thermal Evaporation (열 증착법)

1) 증착이 일어나는 연소실(챔버)을 진공으로 만들어준다.

2) 증착 하고자 하는 시료에 저항열을 가하여 기체로 만든다.

3) 기판에 도착한 기체는 차가운 기판을 만나 응축된다.

4) 기체 문자들이 응축을 거듭하며 박막을 형성한다.

4. E-beam Evaporation

1)열 증착 법의 한계

- 열 증착 법은 Furnace 자체를 가열하므로 부분적인 증발이 어려움.

- 가할 수 있는 온도의 한계가 존재

2) 전자 빔 증착 법(E-beam Evaporation)

5. Sputtering

1) Sputtering 과정

2) DC / RF Sputtering 차이

RF sputtering : 전극이 주파수에 따라 변하며 음극에서 양극으로 바뀌며 부도체에 달라붙지 않고 연속적으로 충돌을 일으켜 부도체로도 증착이 가능.

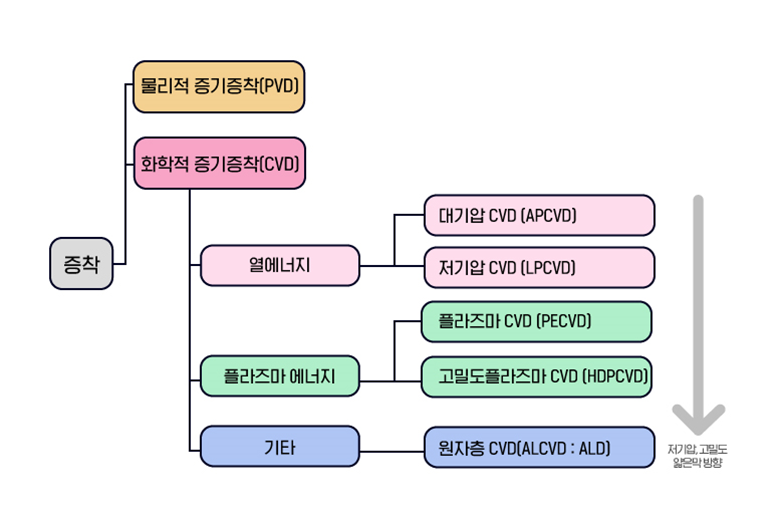

1. CVD란?

- CVD(Chemical Vapor Deposition)란 형성하고자 하는 박막 재료를 구성하는 원소를 포함하는 가스를 기판 위에 공급해 기상 또는 기판 표면에서 화학적 반응으로 박막을 기판에 형성하는 방법.

2. CVD 장점

- PVD보다 표면 접착력이 10배 높음

- 대부분의 표면에 적용 가능하므로 활용도가 높음

- 도체, 부도체, 반도체 박막 증착에 모두 사용가능

- 불순물의 분포와 농도조절 가능

- 반응 가스 선택가능

- 대량생산 가능

3. CVD 단점

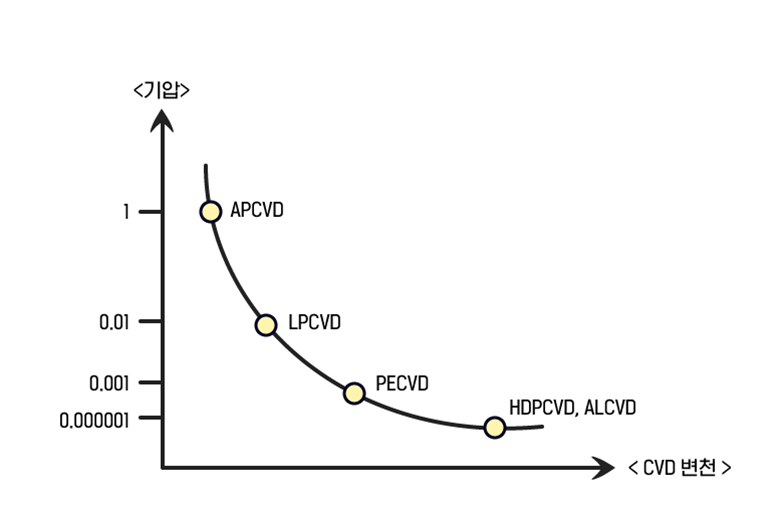

- 압력이 낮을수록 공정의 프로세싱 시간이 길어짐

- 고진공 상태에서 기체들의 반응속도를 유지하려면 웨이퍼 온도를 높여야 하지만, 그러면 재료 선택이 까다로워짐

- 두께 조절 컨트롤하기 어려움

- 반응 변수가 많음

- 위험한 가스의 사용

4. CVD 방식의 종류

- 열에너지 이용 방식 : APCVD(대기압), LPCVD(저기압)

- 플라즈마 에너지 이용 방식 : PECVD(저밀도 플라즈마), HDCVD(고밀도 플라즈마)

- 원자를 표면에 흡착시키는 방식 : ALCVD(원자층 증착방법)

5. CVD 원리

1) 프로세스 챔버 속으로 주입된 반응 가스가 웨이퍼 표면 위로 이동

2) 반응 가스가 표면에 흡착

3) 화학반응을 거쳐 웨이퍼 표면에 고체 상태(막)을 형성하고, 반응 부산물(Byproduct) 생성

4) 반응부산물 가스가 웨이퍼 표면으로부터 탈착하여 프로세스 챔버의 gas stream으로 증발된 후 밖으로 배출

6. ALD(Atomic Layer Deposition) 원리

1) 흡착단계 : 1차 소스(전구체)를 프로세스 챔버에 넣으면 먼저 표면 흡착이 일어난다.

2) 치환단계 : 다른 종류의 2차 소스(반응체)를 넣으면 1차 흡착된 물질과 화학적 치환이 일어난다.

3) 생성단계 : 최종적으로 제3의 신규물질(막)이 생성된다.

4) 배출단계 : 잔류 가스가 배출되어 결국 1개 층만 표면에 흡착되어 달라붙게 된다.

총 4개의 단개가 하나의 사이클로 계속해서 반복하여 layer 두께를 조절할 수 있다.

7. ALD특징

- PVD와 같은 물리적 방식이 아니고, CVD와 유사한 화학적 방식

- 갭이나 트랜치의 벽면에도 잘 달라 붙음

- 섭씨 400도 이하(200~400도)의 낮은 온도에서 공정진행이 가능

1) ALD 장점

- 자기제어반응으로 단위nano 미터급 두께 정밀히 쌓을 수 있음

- 층 내의 전체 격자가 정형적인 각을 이뤄서 질서정연하고 얇은 두께 형성

- 두께 조절에 획기적

- 낮은 온도에서 공정이 가능해 다른 막에 영향을 거의 끼치지 않음

2) ALD 단점

- 1개 사이클에 원자층이 1개 층 씩만 쌓여 속도가 느림

- 저온에서 진행하여 막의 물성이 떨어짐

- 1차 소스와 2차 소스들을 선택하는 데 한정적

3) ALD의 활용

- DRAM의 캐패시터

- 게이트 옥사이드

- 메탈 베리어(Metal Barrier)

- NAND의 3D를 구성하는 가장 중요한 절연 막/금속

| [반도체 8대공정] 7. EDS공정 (0) | 2021.11.29 |

|---|---|

| [반도체 8대공정] 6. 금속 배선 공정 (0) | 2021.11.29 |

| [반도체8대공정] 3. Photo공정 (0) | 2021.11.29 |

| [반도체 8대공정] 2. 산화와 도핑 공정 (0) | 2021.11.29 |

| [반도체 8대공정] 4. 식각공정 (장비구성, 동작원리) (1) | 2021.11.26 |

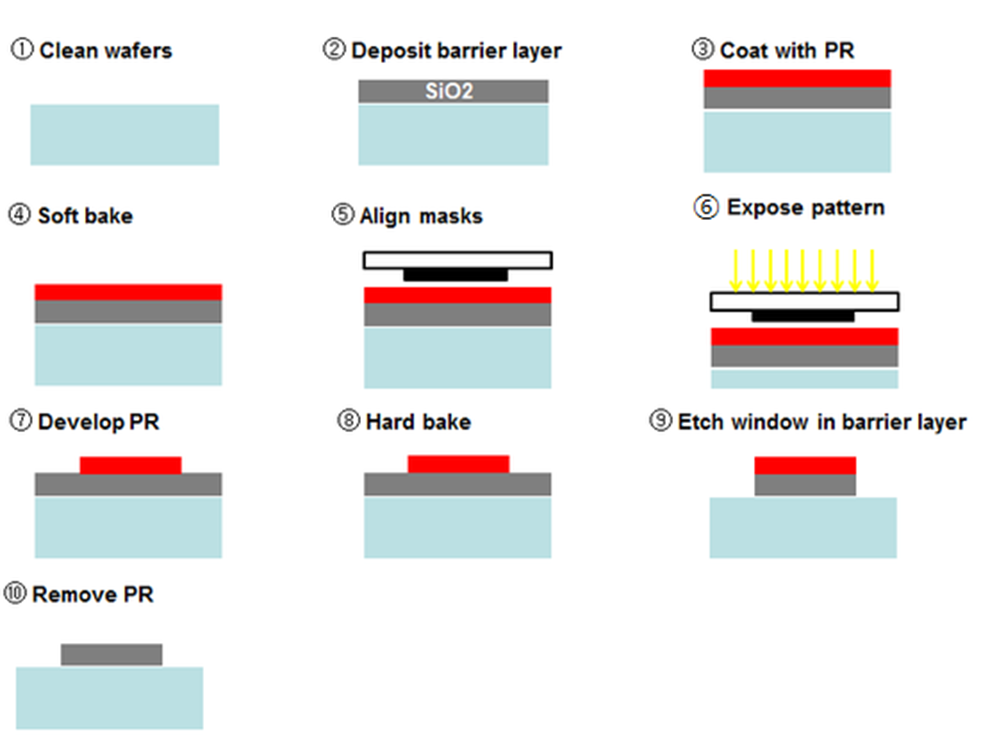

2. Photo 공정의 순서

1) Wafer Cleaning : 불순물로 인해 불량이 생기는 것을 방지

2) De-hydrozation : 눈에 보이지 않는 물기를 제거하기 위해 형태의 90~110도의 장비 위에서 가열하여 남은 액체를 날려보낸다.

3) Spin Coating : 회전기 위에 웨이퍼를 올린 다음 PR을 떨어뜨려 원심력에 의해 PR을 얇게 코팅한다.

4) Soft bake : PR의 접착력을 강화하기 위해 90~100도의 열을 가하여 화학적으로 안정시킨다.

5) Alignment / Exposure : photo mask를 웨이퍼 위의 정확한 위치에 맞춘다. 이 후 PR에 패턴을 새기기 위해 UV를 분광한다.

6) Post-Exposure Bake : 빛은 파장을 지니고 있어 수직으로 물결 모양의 패턴이 새겨지는데 열처리를 가하면 rough한 표면이 부드러워진다.

7) Develop : Exposure에 의해 변성된 PR 부분을 알칼리 용액인 TMAH에 담그면 선택적으로 PR을 제거한 다음 rinsing과 drying을 거친다.

8) Hard Bake : rinsing과정에서 용액을 사용했기 때문에 높은 온도에서 남은 PR 용액과 액체들을 증발시키고 새겨진 패턴 부분을 감싼 PR 부분의 부착을 더욱 견고하게 한다.

3. Photo Resist의 종류

1) Positive PR : Develop 과정에서 UV 광선을 쬔 부분이 녹는 PR

- 산소와 반응하지 않고 비교적 두꺼운 막을 사용해도 좋은 상을 얻는다.

- 접착력이 낮고 Exposure time과 develop에 민감하다.

2) Negative PR : UV를 쬐지 않은 곳의 PR이 녹는 감광액

- Positive PR과 반대 방향으로 패턴이 형성됨.

- 접착력이 높고 Exposure time과 develop에 민감하지 않아 컨트롤 용이

- 산소와 반응하고 독성이 강하며 2um이하 선폭 구현이 어려움.

4. Exposure 방법과 Mask의 종류

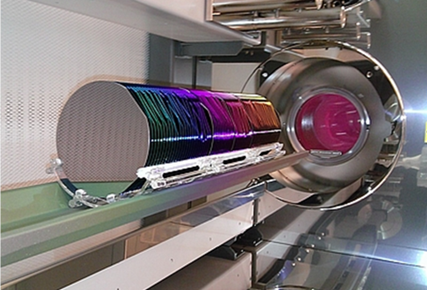

1) Scanner 방법 : Mask와 Wafer의 크기가 같고 스캐너처럼 지나가듯이 빛을 분광한다.

- 생산속도가 빠른 장점

- Mask가 비싼 단점

2) Reduction Stepper 방법 : Mask의 크기를 작게 만들어 Stepper가 움직이며 Wafer에 부분적으로 빛을 분광한다

- Mask의 생산 비용이 적은 장점

- 분광- 이동을 반복하여 공정 소요시간이 오래 걸린다는 단점

5. Photo Lithography의 Key Point

1) CD Control : 설계된 선폭을 얼마나 정확하게 구현할 수 있어야 한다.

2) Overlay/Alignment : 여러 layer를 원하는 위치에 정확히 배치가 가능해야 한다.

3) Defectivity : particle의 존재 자체만으로 Wafer 패턴에 큰 영향을 끼칠 수 있다 -> 당연히 없어야 함.

4) Metrology : mask는 Lithography를 거친 후 저항 패턴과 정확성을 검증해야 한다. -> 마스크 관리가 잘 되어야 함.

5) Cost : 공정이 여러 번 이루어지기 때문에 처리량을 유지하고 높은 수율을 뽑아야 한다.

6. Extreme Ultraviolet (EUV)

1) 공기에 의한 EUV흡수를 막기 위해 진공 상태를 유지해야 한다.

2) 빛 흡수가 큰 렌즈를 대신해 반사를 이용하는 거울을 이용해 광학계를 만든다.

3) 거울의 EUV 흡수 최소화를 위해 몰리브덴과 실리콘층을 층층이 쌓은 다층 박막 거울을 형성해야 한다.

4) 공기와 거울에 96%의 극자외선이 흡수되므로 원하는 만큼의 빛 조사량을 만들기 위해 고에너지의 빛을 만들어줘야 한다.

5) 패터닝을 위한 Reticle은 기존의 투과형이 아닌 새로운 방식의 반사형 마스크를 만들어야 한다.

6) 펠리클은 마스크 바로 앞쪽에 위치해 공정에서 발생하는 particle을 막아주는 방어막 역할을 하는 층이며, 펠리클만 세정해준다면 문제없이 지속 사용이 가능하나 EUV에 적절한 펠리클 물질을 개발해야 한다.

7) 흡수되는 고에너지의 빛은 열에너지로 바뀌는데 이때 노광장비의 온도가 상승하여 부품의 변형(펠리클, 거울, 레티클 등)을 일으켜 고성능의 냉각 시스템 요구한다.

8) 파장이 짧기 때문에 DOF가 적어 나노단위의 Alignment 기술도 중요하다.

| [반도체 8대공정] 6. 금속 배선 공정 (0) | 2021.11.29 |

|---|---|

| [반도체 8대공정] 5. 박막 증착 공정 (0) | 2021.11.29 |

| [반도체 8대공정] 2. 산화와 도핑 공정 (0) | 2021.11.29 |

| [반도체 8대공정] 4. 식각공정 (장비구성, 동작원리) (1) | 2021.11.26 |

| [반도체 8대공정]4. 식각공정(ICP, CCP, 공정 불량 이슈와 해결법) (0) | 2021.11.25 |

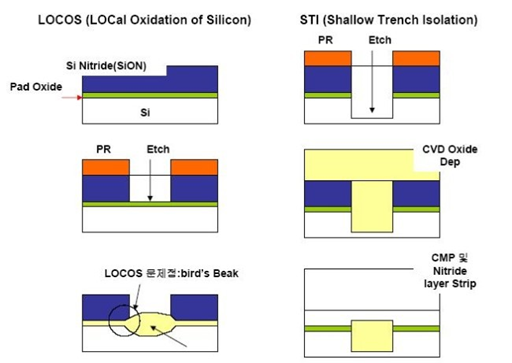

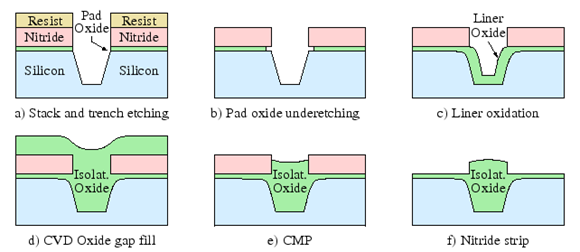

1.산화(Oxidation)란? : 산화란 산소와의 결합, 수소의 떨어져 나감, 전자 수가 줄어듦을 의미하며, 환원은 산소와의 분리, 전자 수가 늘어남을 의미한다.

2. 반도체에서 산화(Oxidation)란? : 일반적으로 실리콘 표면에 이산화실리콘(SiO2)를 형성하는 것 = 산화막을 형성하는 것.

3. 산화막의 용도 :

4. 산화막의 방법과 종류:

5. 산화 메커니즘

6. 산화에 영향을 미치는 요인

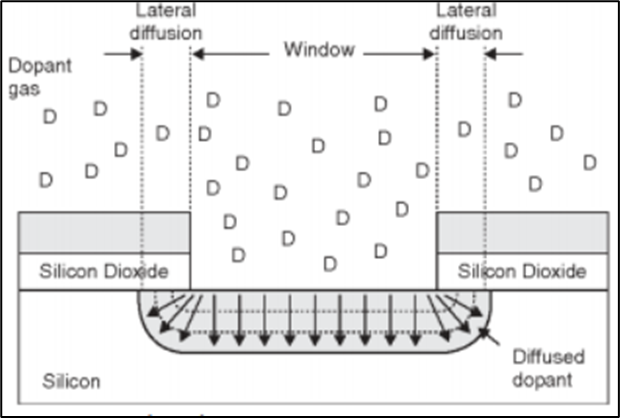

1. 도핑 – 확산(Diffusion) 공정 :

1) 전부착 단계(Pre-Deposition)

- 실리콘 웨이퍼 안으로 불순물 주입

- 800 ℃ ~ 1100 ℃

2) 드라이브인 단계(Drive-In)

- 열처리를 가해 불순물을 활성화시킴

- 주입 깊이 및 농도 조절

- 1000 ℃ ~ 1200 ℃

1) Constant Source Diffusion(고정 소스 확산)

- 상대적 긴 Pre-dep. + 짧은 Drive-in

- pre-dep를 오래 하면 상보에러함수 형태를 띰

-표면 농도가 일정한 상태로 유지되게 함

- 외부에서 dopant를 지속적으로 공급

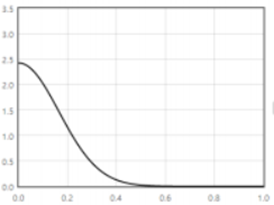

- 상보에러함수 형태의 확산식

2) Limited Source Diffusion(제한 농도 조건)

- 짧은Pre-dep . + 상대적으로 긴 Drive-in

- drive-in을 오래하면 가우시안 분포 형태를 띰

- 전체 도핑된 dopant 양이 일정함.

- 외부 dopant의 공급 없음

- 가우시안 분포의 확산식

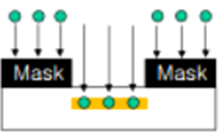

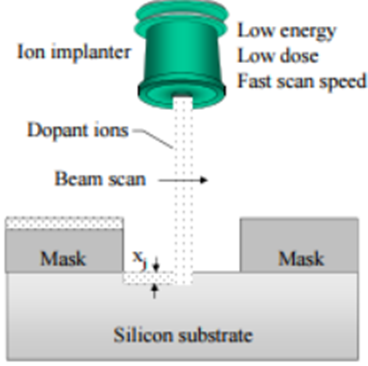

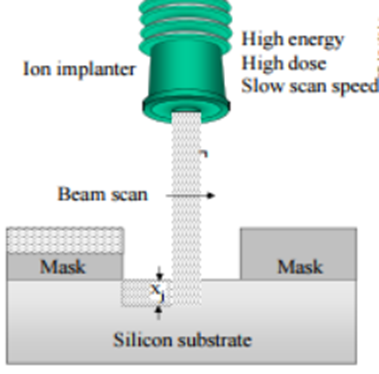

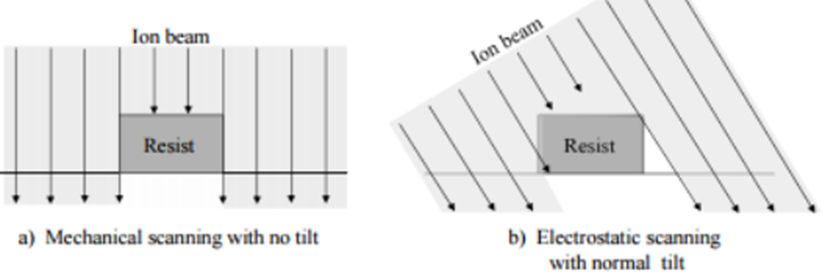

1. 도핑 – 이온 주입(Ion Implantation) 공정

1) 이온 주입(Ion Implantation)

- 가속시킨 이온을 원하는 위치에 강제로 주입함

- 마스킹 레이어로 질화막, 산화막, PR을 사용함

2) 드라이브인 단계(Drive-In)

- 주입된 이온을 활성화 시킴

- 두께 및 농도 제어

- 1000 ℃ ~ 1200 ℃

- RTA(Rapid Thermal annealing)라고도 불리며, 고온이고 아주 빠르게 진행함

| [반도체 8대공정] 5. 박막 증착 공정 (0) | 2021.11.29 |

|---|---|

| [반도체8대공정] 3. Photo공정 (0) | 2021.11.29 |

| [반도체 8대공정] 4. 식각공정 (장비구성, 동작원리) (1) | 2021.11.26 |

| [반도체 8대공정]4. 식각공정(ICP, CCP, 공정 불량 이슈와 해결법) (0) | 2021.11.25 |

| [반도체 8대공정] 4. 식각공정(공정) (1) | 2021.11.25 |

[식각장비 시스템 구성]

1. 전원 공급과 시스템 제어를 담당하는 제어부

2. 메인 프레임을 구동시키는 구동부

3. 메인프레임 안에 있고 공정이 이뤄지는 챔버

4. 웨이퍼 척의 온도를 조절하는 온도 조절부 (TCU : Temperature Control Unit)

5. 부수적 모듈 성분

6. 유틸리티부

7. 조절 기기

가스의 유량을 전기적으로 조절하는 MFC (Mass Flow Contoller)

[모듈 배치]

[공정 챔버]

[온도 제어부 TCU]

1. 온도 제어 장치의 역할

2. 사용처

3. 동작 원리

[진공 펌프]

1. 역할

2. 펌프별 특징과 구성 [드라이, 부스터 펌프]

3. 펌프별 특징과 구성 [터보 펌프]

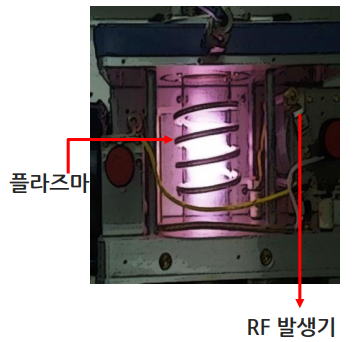

[RF 발생기]

1. 역할

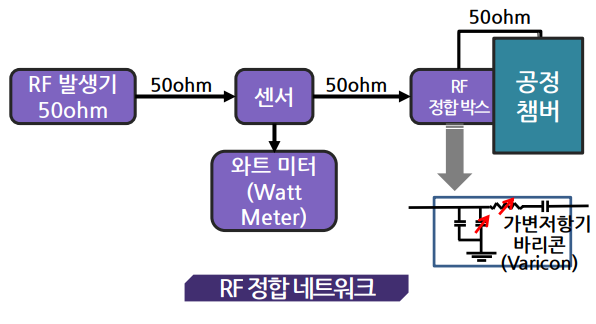

[RF 정합기]

1. 역할

2. RF정합 네트워크가 50ohn을 유지하는 이유

| [반도체8대공정] 3. Photo공정 (0) | 2021.11.29 |

|---|---|

| [반도체 8대공정] 2. 산화와 도핑 공정 (0) | 2021.11.29 |

| [반도체 8대공정]4. 식각공정(ICP, CCP, 공정 불량 이슈와 해결법) (0) | 2021.11.25 |

| [반도체 8대공정] 4. 식각공정(공정) (1) | 2021.11.25 |

| [반도체 8대공정]1. Wafer 제조공정 (0) | 2021.11.18 |