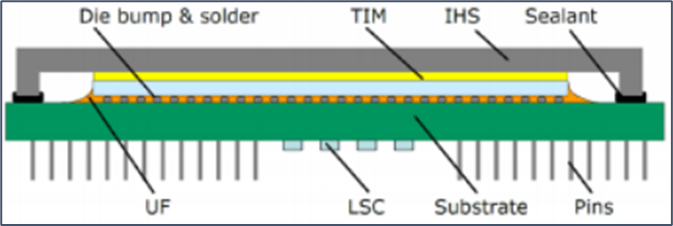

- 전공정을 거친 후 낱개로 잘린 칩, 즉 Die는 외부와 전기신호를 주고받을 수 없으며, 외부 충격에 의해 손상되기 쉽다. 즉 반도체 칩을 기판이나 전자기기에 장착하고 칩이 외부와 신호를 주고받을 수 있도록 길을 만들고 보호해주는 과정을 패키징(Packaging)이라 한다.

2. 패키징 과정

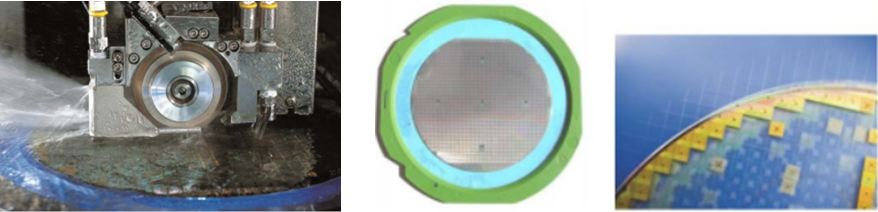

2-1. 웨이퍼 절단(Wafer Sawing)

웨이퍼를 낱개의 칩으로 분리하는 단계로 스크라이브 라인(Scribe Line)을 따라 웨이퍼를 다이아몬드 톱이나 레이저를 이용하여 절단한다.

2-2. 칩 접착(Die attach)

절단된 칩을 반도체 칩을 외부 회로에서 전기신호를 전달하고 보호해주는 리드프레임 또는 PCB로 옮긴다

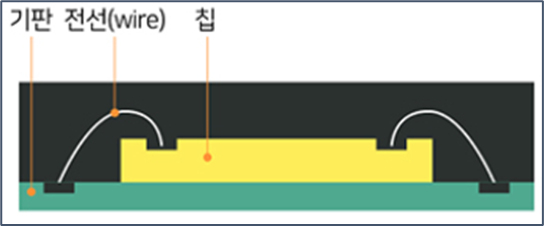

2-3. 금속 연결(Wire Bonding)

2-4. 성형 공정(Molding)

2-5. 패키지 테스트 공정(Package Test)

- 테스트를 거쳐서 다양한 환경에서 칩의 신뢰성을 검증하고 그 과정에서 생긴 주요 이슈는 제조공정이나 조립 공정에 전달해 사전에 오류를 방지해 제품의 질을 향상시킬 수 있도록 한다.

• 제조공정이나 조립공정에 피드백 ▶ 제품 질 향상

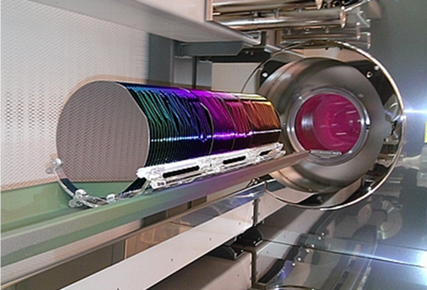

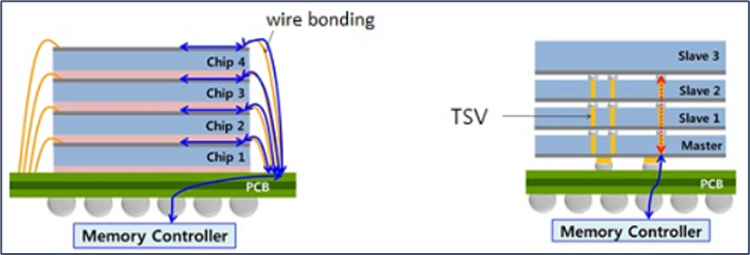

- TSV(Through Silicon Via)공정은 와이어를 이용해 칩을 연결했던 적층 기술인 wire bonding을 대체하는 기술로, 칩에 미세한 구멍(Via)를 뚫어 상,하단 칩을 전극으로 연결하는 패키징 기술이다.

2. TSV의 장점

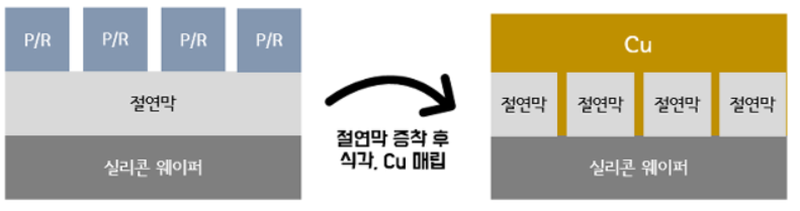

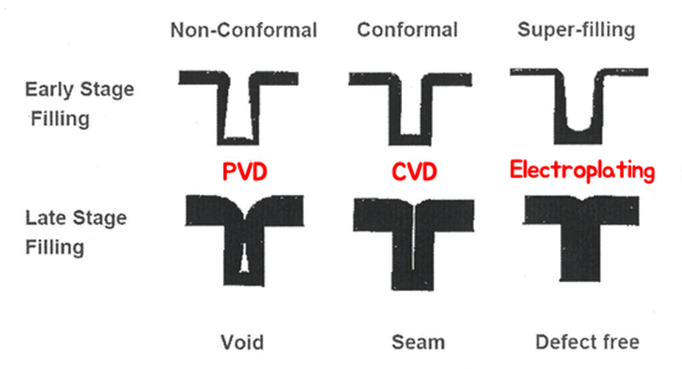

- TSV는 실리콘 웨이퍼(silicon wafer)를 관통하는 미세 홀(via)을 형성한 후, 홀 내부에 전도성 물질(conductive materials)을 충전시켜 칩 내부에 직접적인 전기적 연결 통로를 확보하는 기술로, 칩 내부에 직접 연결 통로가 확보되기 때문에 다수의 칩을 수직으로 적층할 때 와이어 본딩을 이용한 3차원 패키징에서의 I/O(input/output unit) 수의 제한, 단락 접촉 불량과 같은 문제점을 해결할 수 있다.

- 추가적인 공간을 요구하지 않아 패키지 크기 소형화 가능

- 칩 간의 상호 접속(Interconnection) 길이를 감소시킬 수 있어 빠른 신호전달, 고용량, 저전력

3. TSV의 적용 분야

4. TSV의 요구 기술

5. TSV의 기술 동향

- 사람 머리카락 굵기의20분의 1 수준의 수 um직경의 통로 6만개를 만들어 오차 없이 연결하는 첨단 패키지 기술 이를 바탕으로 한 HBM-PIM을 제작해 세계최초 인공지능 연산용 가속기가 포함된 메모리를 만들어 기존 HBM2 대비 2배의 성능, 70% 저하된 전력 사용율을 개발

- HBM2보다 처리속도가 50% 빠르게 만들었다. 메모리 칩을 모듈로 만들어 메인보드에 붙이는 방식이 아니라 칩 자체를 GPU같은 로직에 수십 um간격으로 장착해 더 빠른 데이터 처리가 가능.

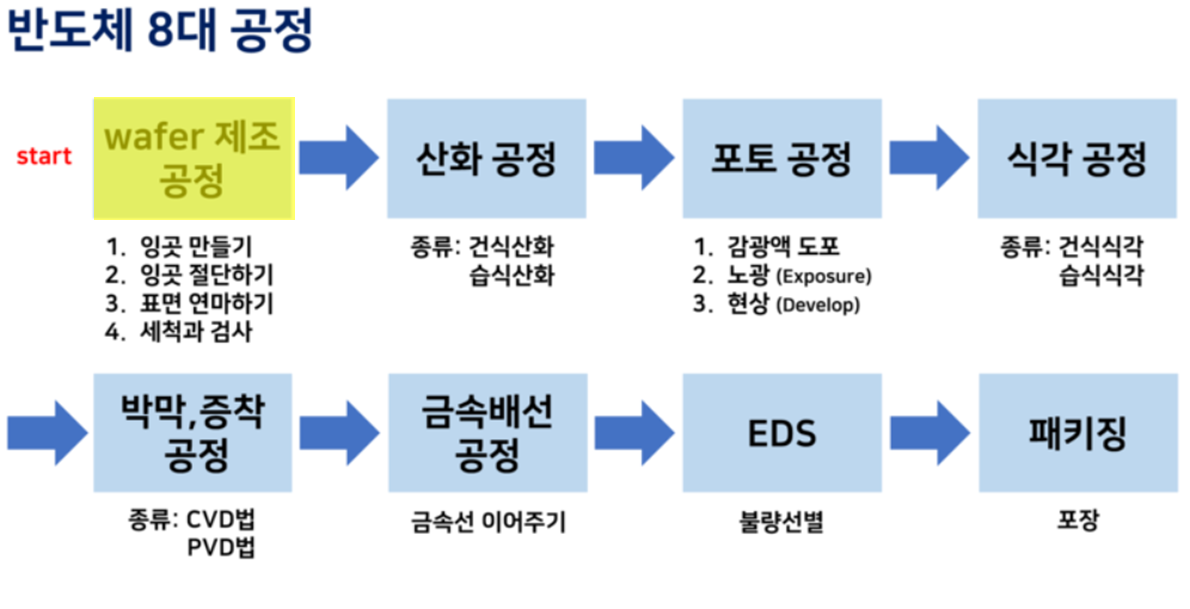

'반도체 8대공정' 카테고리의 다른 글

| [반도체 8대공정] 7. EDS공정 (0) | 2021.11.29 |

|---|---|

| [반도체 8대공정] 6. 금속 배선 공정 (0) | 2021.11.29 |

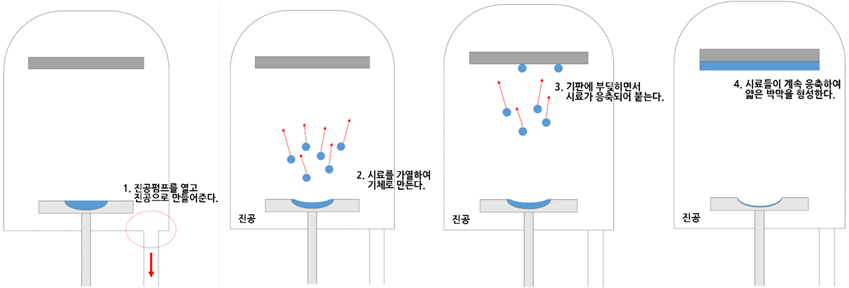

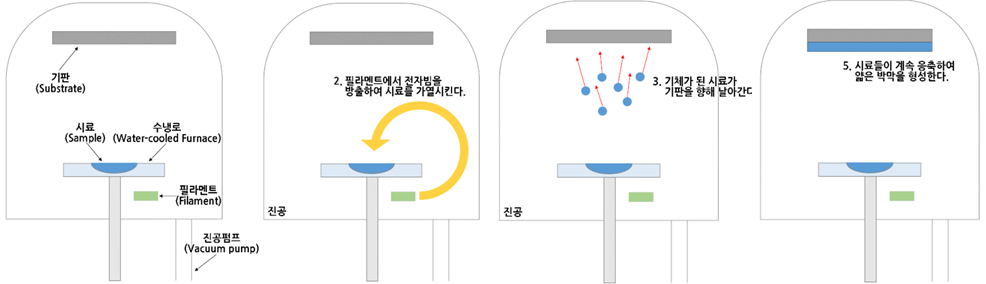

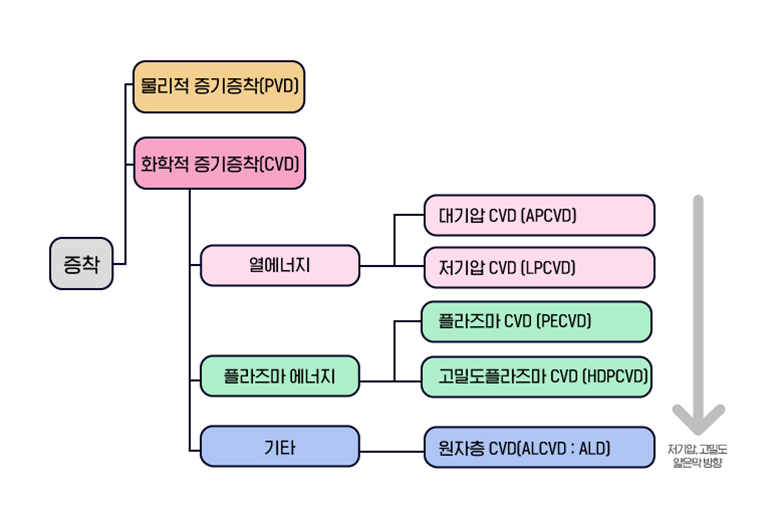

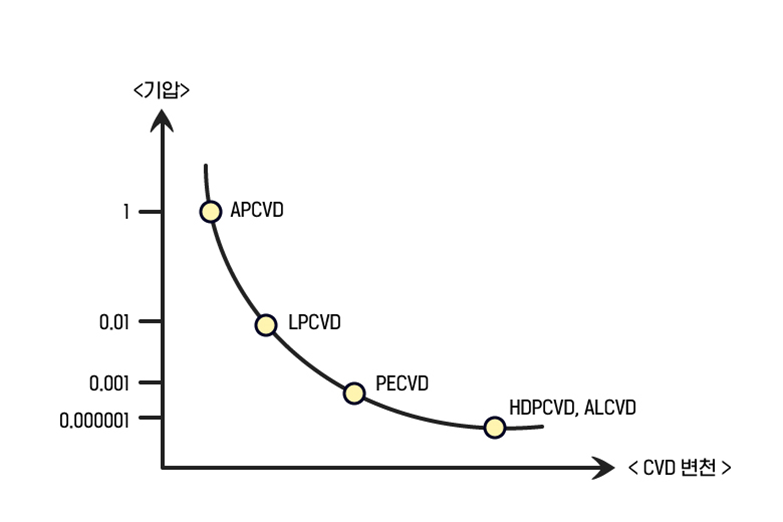

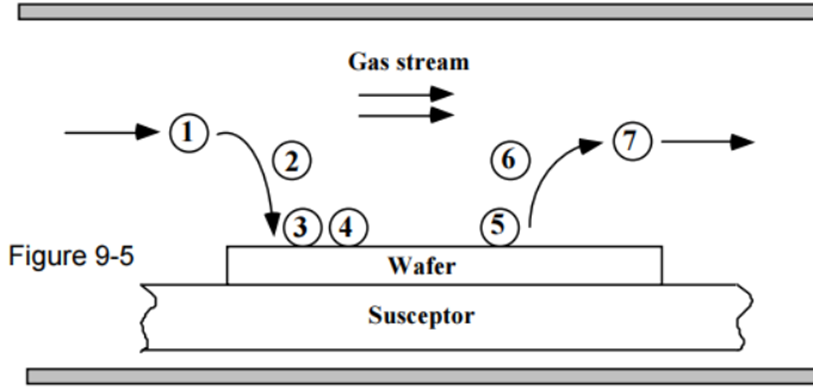

| [반도체 8대공정] 5. 박막 증착 공정 (0) | 2021.11.29 |

| [반도체8대공정] 3. Photo공정 (0) | 2021.11.29 |

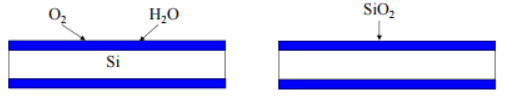

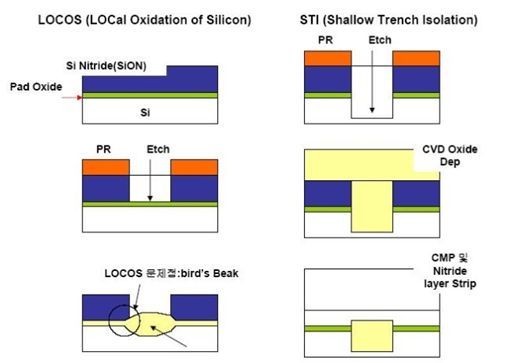

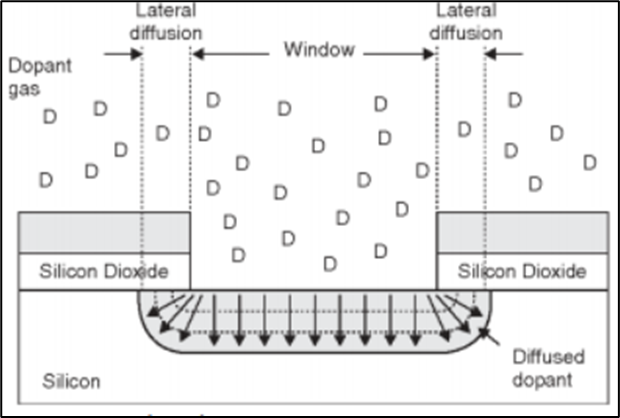

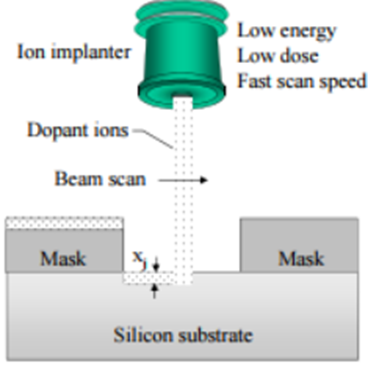

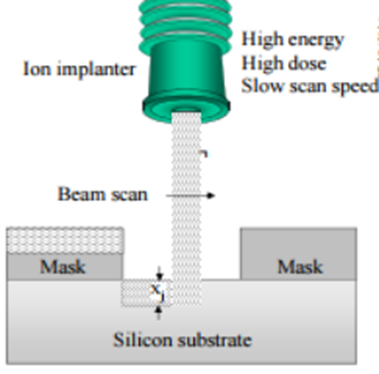

| [반도체 8대공정] 2. 산화와 도핑 공정 (0) | 2021.11.29 |